Dong Du, Xu Lu, Erhu Feng, Bicheng Yang, Yubin Xia, Haibo Chen IPADS, Shanghai Jiao Tong University

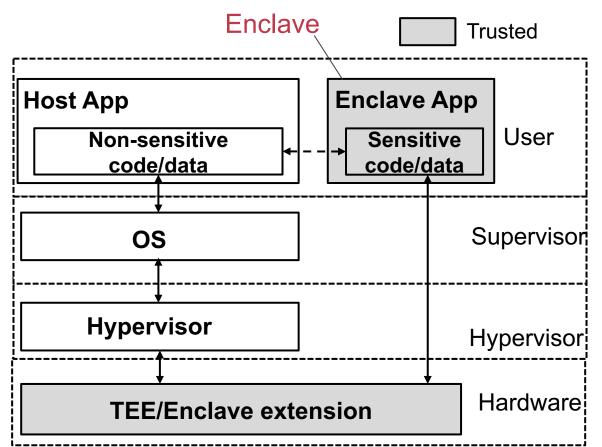

## What's Enclaves?

Hardware-assisted Trusted Execution Environment

## Why Enclave for RISC-V?

#### Lessons learned:

Security is a necessary processor need

#### User needs:

Users will run sensitive code/data in RISC-V

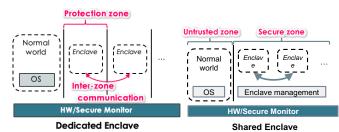

## Why Another Enclave?

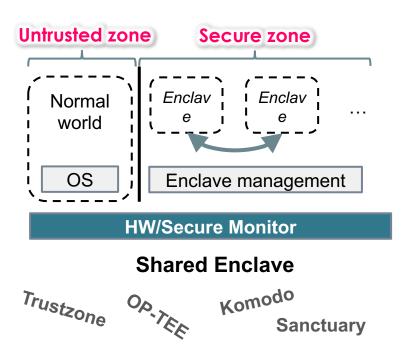

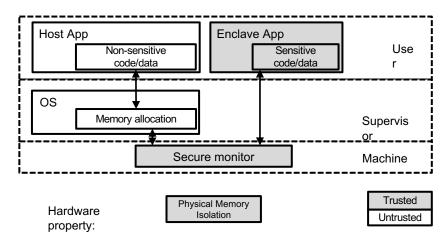

Shared Enclave Architecture: A single HWassisted protection zone for multiple enclaves

- Pros: low communication latency (intra-zone)

- Cons: higher TCB •

#### **HW/Secure Monitor**

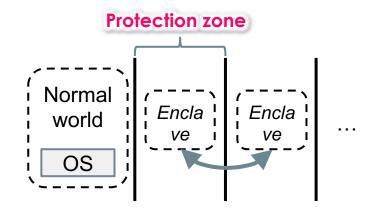

#### **Dedicated Enclave**

SEV-ES SGX Haven HexFive Graphene-SGX Keystone SEV TIMBER-V Sanct Sanctum

#### Dedicated Enclave Architecture: A single HWassisted protection zone for a single enclave

- **Pros:** small TCB  $\rightarrow$  higher security-assurance

- Cons: long communication latency (inter-zone) & non-scalable

## Why Another Enclave?

En

| SGX Intel Nication boot number & gran (PT/Cache) integrity   SGX Intel Slow X Unlimited 256MB X Small √ | Systems |          | Performance |      |   |           | Security |   |       |                        |

|---------------------------------------------------------------------------------------------------------|---------|----------|-------------|------|---|-----------|----------|---|-------|------------------------|

|                                                                                                         | Туре    | Name     | Arch        |      |   |           |          |   | тсв   | Mem enc./<br>integrity |

| Howen Intel Class V Halinsted OCOMD V Lange J                                                           |         | SGX      | Intel       | Slow | X | Unlimited | 256MB    | X | Small | $\checkmark$           |

| naveni intei Siow X Unimited 256MB X Large V                                                            |         | Haven    | Intel       | Slow | X | Unlimited | 256MB    | X | Large | $\checkmark$           |

| Graphene Intel Slow X Unlimited 256MB X Large √                                                         |         | Graphene | Intel       | Slow | X | Unlimited | 256MB    | X | Large | $\checkmark$           |

# Existing enclave systems can not achieve security and performance simultaneously.

| Shared          | TrustZone | ARM    | Fast | X            | Unlimited | All | Partial      | Large | X |

|-----------------|-----------|--------|------|--------------|-----------|-----|--------------|-------|---|

|                 | OP-TEE    | ARM    | Fast | X            | Unlimited | All | Partial      | Large | X |

| Enclave         | Komodo    | ARM    | Fast | $\checkmark$ | Unlimited | All | Partial      | Medi. | X |

|                 | Sanctuary | ARM    | Fast | $\checkmark$ | Unlimited | All | Partial      | Large | X |

| heavy.LIG<br>HT | Penglai   | RISC-V | Fast | $\checkmark$ | Unlimited | All | $\checkmark$ | Medi. | X |

- SW-HW Co-design Trusted Execution Environment (TEE)

- Based on RISC-V ISA

- Can run on any RISC-V core that supports Privileged ISA v1.10

- IoT and Cloud

- Trusted Code Base

- RISC-V core (PMP/sPMP) + Verifiable security monitor (M-mode privilege) + TEEOS

- Secure Assurance

- Strong isolation between enclave and other application or OS

- Protect against a malicious or compromised OS

- Secure boot and remote attestation for chain of trust

- High performance and scalability

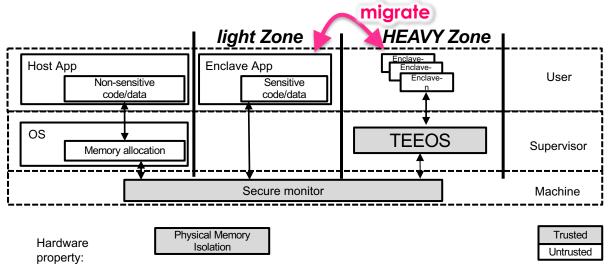

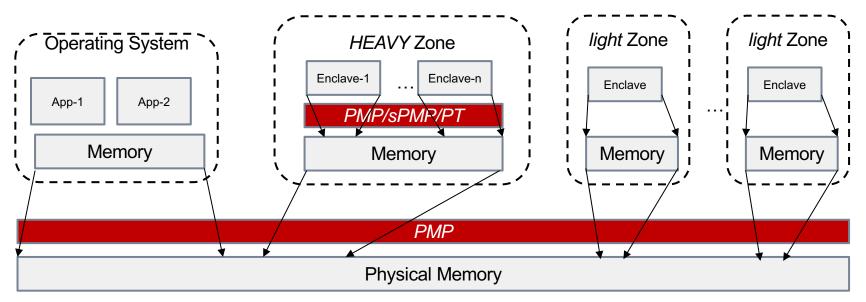

### Penglai with heavy.LIGHT Architecture

#### heavy.LIGHT architecture

- LIGHT Zone: A dedicated HWisolated box for a single enclave

- heavy Zone: Multiple-Enclaves isolated through TEEOS

- **TEEOS:** Leverage s-mode for enclave isolation (sPMP and PMP)

- Fast cross-enclave communication (IPC)

- Flexible resource management

- Fast startup

- Scalable instances

### heavy.LIGHT Architecture

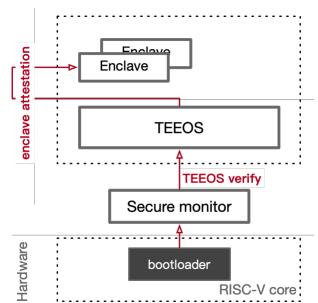

#### • Security monitor:

- A small software running on M-mode

- Enclave measurement and attestation

- Manage enclave and provide isolation via physical memory isolation property

#### Physical Memory Isolation Property

- Restrict physical memory access of S- or U-mode software

- Dynamically configurable by security monitor

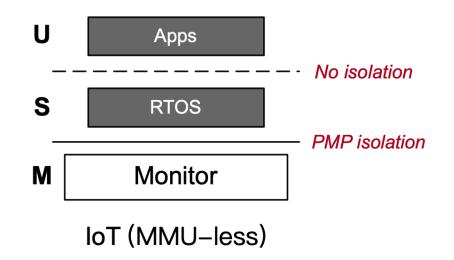

### Hardware Requirement

- RV32 or RV64

- All of the three modes (M/S/U)

- Support RISC-V priv. ISA v1.10

- need sPMP or PT support for performance

- Larger, tamper-proof boot ROM (~1MB)

- Trusted bootloader should be added to initialize the system

- Physical memory isolation support

- New hardware property for memory isolation

- IOPMP extension

- Defend malicious I/O access

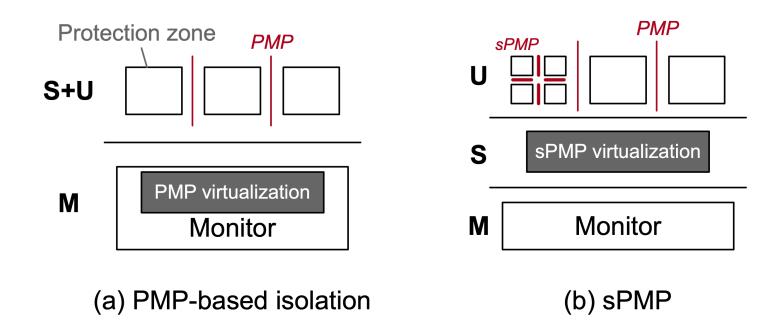

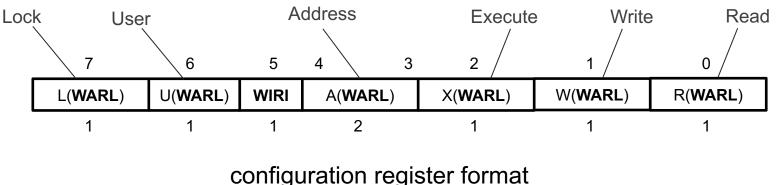

## SPMP (S-mode PMP)

- For IoT devices (MMU-less)

- it is desirable to enable S-mode OS to limit the physical addresses accessible by U-mode software

## SPMP (S-mode PMP)

• S-mode virtualization for scalable enclaves

- sPMP entries

- 8-bit configuration register

- XLEN-bit address register

0

address[33:2] (WARL)

address register (RV32)

- sPMP entries

- 8-bit configuration register

- XLEN-bit address register

| 31 24     | 23 16     | 15 8      | 7         |          |

|-----------|-----------|-----------|-----------|----------|

| spmp3cfg  | spmp2cfg  | spmp1cfg  | spmp0cfg  | spmpcfg0 |

| 31 24     | 23 16     | 15 8      | 7 0       |          |

| spmp7cfg  | spmp6cfg  | spmp5cfg  | spmp4cfg  | spmpcfg1 |

| 31 24     | 23 16     | 15 8      | 7 0       |          |

| spmp11cfg | spmp10cfg | spmp9cfg  | spmp8cfg  | spmpcfg2 |

| 31 24     | 23 16     | 15 8      | 7 0       |          |

| spmp15cfg | spmp14cfg | spmp13cfg | spmp12cfg | spmpcfg3 |

configuration register (RV32)

- sPMP entries

- 8-bit configuration register

- XLEN-bit address register

- Address matching

- Same as PMP

- Locking and privilege mode

- The Lock bit indicates: the sPMP is locked to S-mode

- Priority and Matching Logic

- The lowest-numbered sPMP entry

- Failed accesses generate a page fault exception

Refer our proposal in **RISC-V/TEE** group for details !

## **SMAP and SMEP**

- SMAP (Supervisor Memory Access Prevention)

- leverage the SUM bit in the status register

- SUM=0:

- S-mode memory accesses to memory for U-mode (U=1) will fault

- SUM=1:

- these accesses are permitted

- SMEP (Supervisor Memory Execution Prevention)

- Do not allow the S-mode to execute codes in physical memory that are for U-mode (U=1)

- Violations will trigger page faults

## Chain of Trust: (1) Secure Boot

- The manufacturer provisions:

- device key pair {SK<sub>DEV</sub>, PK<sub>DEV</sub>}

- endorses the certificate

- During CPU resets: load bootloader from boot ROM and execute it

- The bootloader measures and signs the security monitor

- The secure monitor measures and signs the TEEOS

- The user can remotely attest the security monitor and TEEOS by

- trusting the manufacturer's certificate

- comparing the measurement

- and verifying the signature with  $\mathsf{PK}_{\mathsf{DEV}}$

#### Chain of Trust: (2) Remote Attestation for light Zone

- (1) The bootloader provisions the attestation key pair  $\{SK_{SM}, PK_{SM}\}$

- (2) The user uploads an executable to the system

- (3) The user asks SM to create an enclave and initialize it with the executable

- (4) The user asks SM to measure the initial state of the enclave

- (5) The SM measures the enclave, and signs it with the attestation private key

- The user can remotely attest the enclave by

- comparing the measurement

- and verifying it with  $\mathsf{PK}_\mathsf{SM}$

### Chain of Trust: (3) Remote Attestation for HEAVY Zone

- Same (1)-(4)

- (5) The SM measures the enclave through (verified) TEEOS, and signs it with the attestation private key

- The user can remotely attest the enclave by

- comparing the measurement

- and verifying it with  $\mathsf{PK}_\mathsf{SM}$

### **Layered Memory Isolation**

- HEAVY.light provides a strong and flexible physical memory isolation

- RISC-V Physical Memory Protection (PMP)

- PT / S-mode PMP\* for TEEOS memory isolation

\* : need HW extensions in HEAVY.light enclave design

Monitor starts

Untrusted App starts

#### Platform

- N200 from NUCELI (芯来)

- RV32 with sPMP support

- No paging

Enclave executes

| ይ | 芯来科技<br>NUCLEI |  |

|---|----------------|--|

|   |                |  |

N200

- Enclaves chain

- Up to 100 enclaves

| ILog] Blackwater init start                                                 |              |

|-----------------------------------------------------------------------------|--------------|

| In the ret_to_payload, the payload addr is<br>Untrusted is invoking enclave | s 0x80006000 |

| EnclaveLid:0」 handle request                                                |              |

| <pre>Enclave[id:0] starts to invoke Enclave[id</pre>                        | :1]          |

| <pre>Enclave[id:1] handle request</pre>                                     |              |

| Enclave[id:1] starts to invoke Enclave[id                                   | :2]          |

| <pre>Enclave[id:2] handle request</pre>                                     |              |

| Enclave[id:2] starts to invoke Enclave[id                                   | :3]          |

| Enclave[id:3] handle request                                                |              |

| Enclave[id:3] starts to invoke Enclave[id                                   | :47          |

| Enclave[id:4] handle request                                                |              |

| Enclave[id:4] starts to invoke Enclave[id                                   | :5]          |

| <pre>Enclave[id:5] handle request</pre>                                     |              |

| <pre>Enclave[id:5] starts to invoke Enclave[id</pre>                        | :6]          |

|                                                                             |              |

| Enclave[id:97] handle request                                               |              |

| Enclave[id:97] starts to invoke Enc                                         | avo [id·08]  |

|                                                                             |              |

| Enclave[id:98] handle request                                               |              |

| Enclave[id:98] starts to invoke Enc                                         | clave[id:99] |

| Enclave[id:99] handle request                                               |              |

| Enclave[id:99] starts to invoke Enc                                         | laveFid:100  |

| /es Enclave[id:100] handle request                                          |              |

### Conclusion

Light zone

Sensitive

code/data

Secure monitor

Enclave

Host App

OS

Non-sensitive

code/data

Memory allocation

#### Background

- Existing enclave systems is either *dedicated enclave* or *shared enclave*

- Cannot achieve both security & performance simultaneously

- Penglai-Enclave is based on heavy.LIGHT

#### architecture

- Using light-zone and heavy-zone to achieve both performance and security

- TEEOS for scalability

- Cases

- siFive U500 (Xilinx VC707)

- Nuclei N200

Heavy zone

TEEOS

Enclave-n

User

Supervisor

Machine