# 130nm高可靠SOI嵌入式RISCV处理器研究

作者: 乔冰涛, 周墨, 郑云龙, 单毅, 董业民

1.信息功能材料国家重点实验室(中国科学院上海微系统与信息技术研究所)

2. 材料与光电研究中心 (中国科学院大学)

3.芯可方科技(上海)有限公司

报告人: 郑云龙

2019-11-11

#### **Outline**

#### 口本论文的工作

- > 背景简介

- > 空间辐射效应分析与工艺、设计加固

- > 高可靠嵌入式RISC-V处理器设计与实现

#### 1. 背景介绍

- □ 精简指令计算机RISC (Reduced Instruction Set Computing) 在航天电子系统中有着非常广泛的应用。

- □ 从国际上来看,在高可靠处理器领域,目前主要有NASA使用的PowrePC架构CPU和欧洲航空局的SPARC V8架构CPU;从国内来看,主要有龙芯的MIPS架构CPU和北京微电子技术研究所的SPARC V8架构CPU。它们都是基于RISC技术的处理器架构,因此可以说RISC处理器技术是现代航天电子系统的基础。

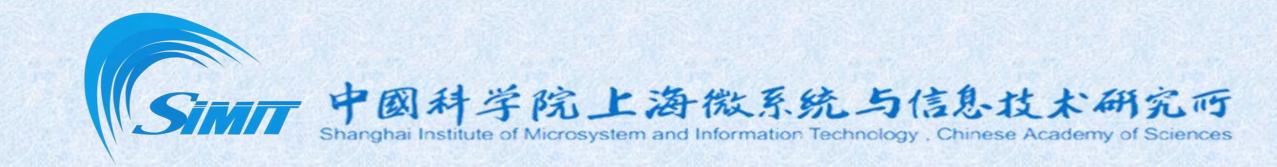

#### 2. 空间辐射环境

空间辐射环境主要包括三个方面的辐射。

□ 地磁捕获的辐射源: 其主要为内外范艾伦 (Van Allen) 辐射带。

□宇宙射线: 其包括银河宇宙射线, 太阳射线和地球射线。

□太阳风暴: 主要是由太阳向外溅射的质子、电子和高能重离子, 通常为高通量, 也

被称为太阳粒子事件,是软错误的重要来源。

#### 2. 空间辐射效应

在复杂的空间工作环境中,处理器芯片容易受到空间高能粒子的影响产生辐射效应,会造成整个芯片工作错误甚至是失效。辐射效应主要分为单粒子效应SEE(Single Event Effect)和总剂量效应TID(Total Ionizing Dose)。常见的SEE又有单粒子闩锁SEL(Single Event Latchup)和单粒子翻转SEU(Single Event Upset)。

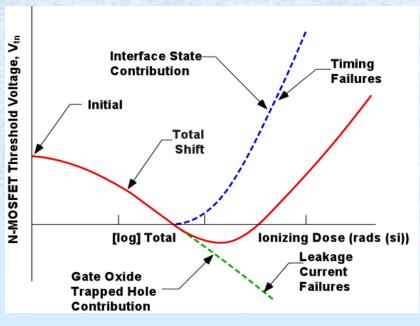

## 2. 总剂量效应TID(Total Ionizing Dose)

总剂量效应(TID)是由于高能光子、高能粒子辐射使晶格中的原子发生位移,或产生电子-空穴对,会在半导体器件的二氧化硅层中产生固定氧化物电荷和界面陷阱电荷,这两种辐射诱生电荷会对器件的参数及功能产生影响,如:MOS晶体管的阈值电压漂移、关态漏电流增加、噪声增加和电子迁移率降低等等。而对于CMOS电路来讲,则会有输出电压下降、静态功耗降低和传输延迟时间增加等影响

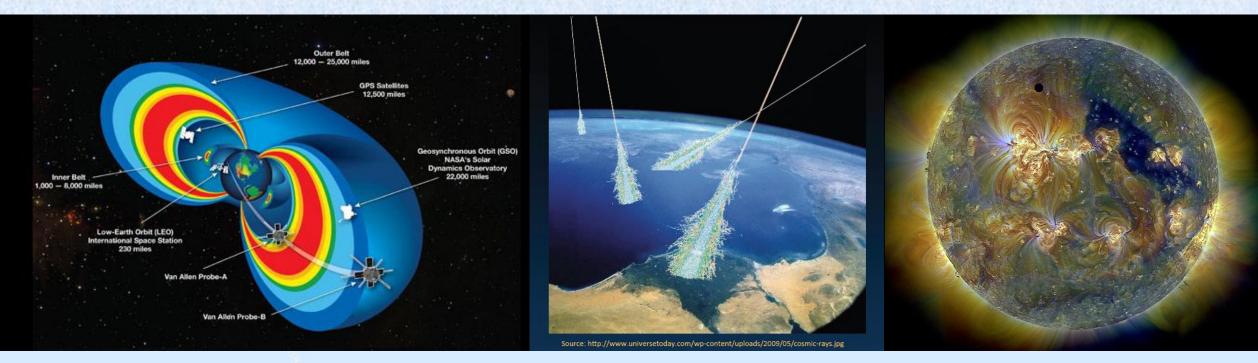

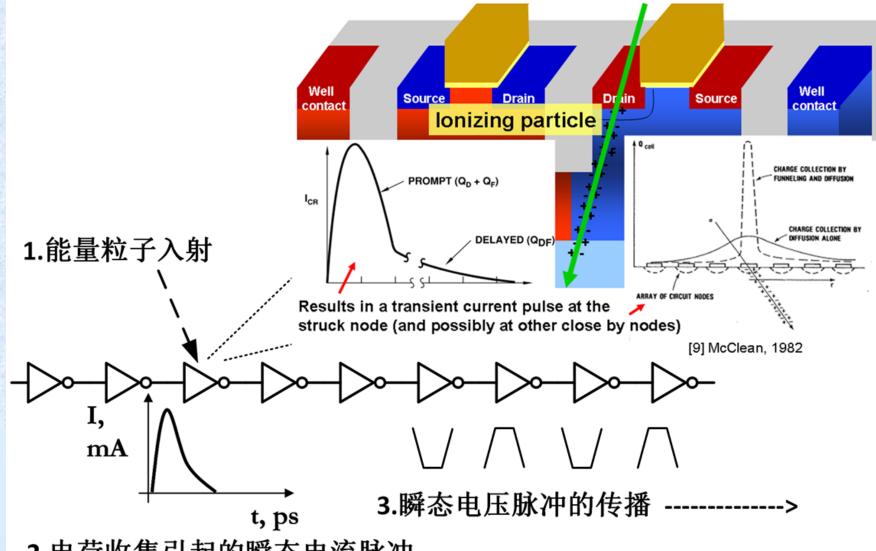

## 2.单粒子翻转SEU( Single Event Upset)

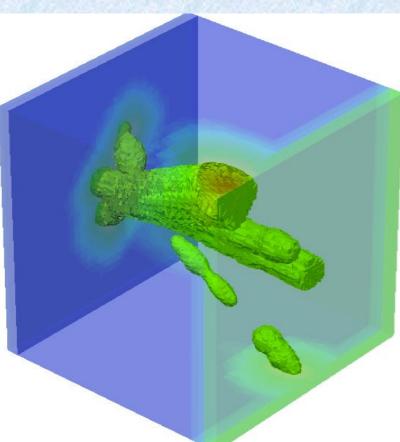

单粒子效应主要来自 于能量粒子穿过集成 电路的半导体或绝缘 体材料而产生, SEU 是由高能粒子轰击晶 体管单元,导致存储 的数据发生翻转。这 种效应不是永久破坏 性的,通过刷新重写 可以恢复原来的状态, 属于软故障。

2.电荷收集引起的瞬态电流脉冲 导致节点电压发生翻转

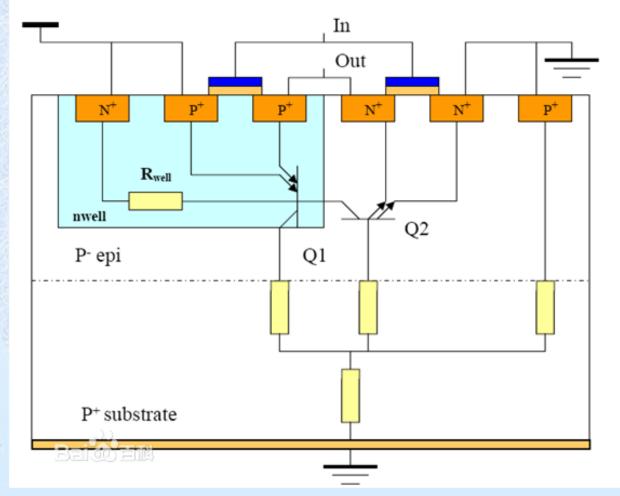

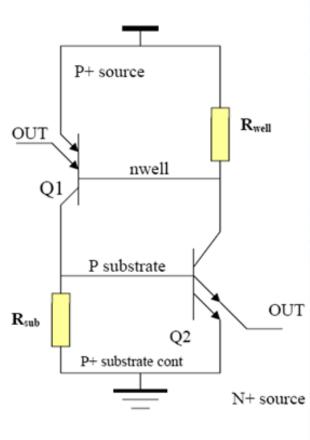

## 2.单粒子闩锁SEL(Single Event Latchup)

SEL是高能粒子触发体 硅CMOS电路的寄生 BJT三极管开启,具有 正反馈回路的闩锁电 路导通,使得局部大岛 路导通,使得局部大岛 路导通,使得局部大岛 游上,使得一个。 进而会造成电子器, 被烧毁,产生不可逆的损害。

NMOS的有源区、P衬底、N阱、PMOS的有源区构成的n-p-n-p结构成的n-p-n-p结构产生的,当其中一个三极管正偏时,就会构成正反馈形成闩锁。

CMOS INV与其寄生的BJT截面图

寄生BJT形成SCR的电路模型

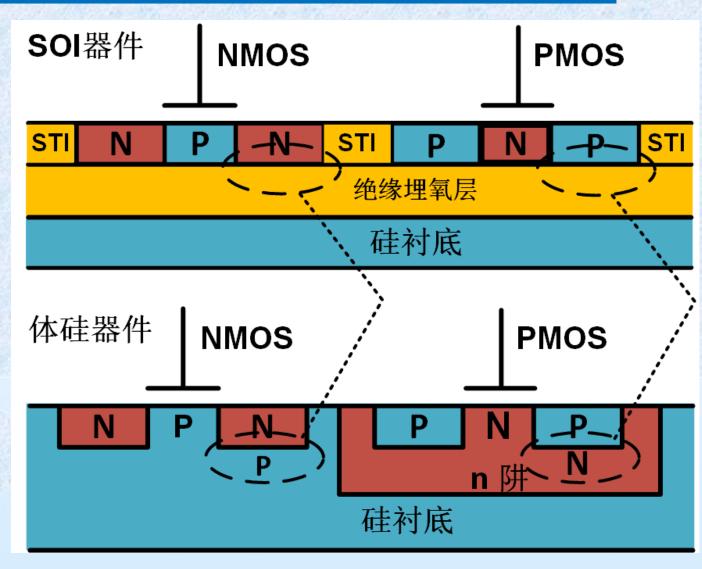

#### 2. 130nmSOI高可靠器件工艺平台

SOI (绝缘体上硅) 是一种由顶层硅、 埋氧层和衬底硅构成的多层三明治结构, 具有速度快、功耗低、射频性能 优越等特点, 被广泛应用于航天等高 可靠领域。

和体硅电路相比,对于SOI器件,由于由于顶层硅很薄和全介质隔离,每个晶体管通过介质与相邻的晶体管隔开,阻止了典型的闩锁通道,消除了体硅器件中的寄生PNPN闩锁结构,因此SOI技术具有天然抗SEL的优势,单粒子翻转(SEU)性能和瞬态效应也显著提高。

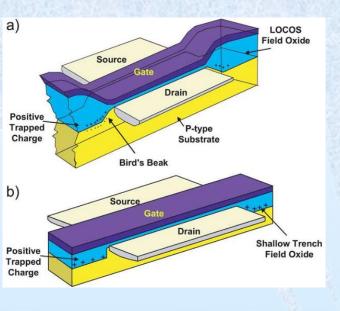

#### 2. SOI平台总剂量效应工艺加固

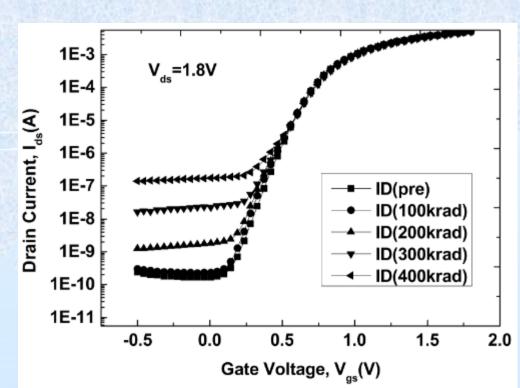

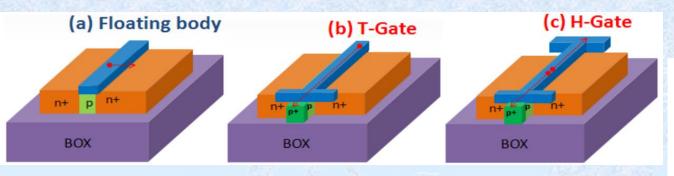

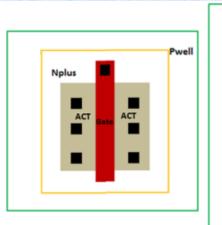

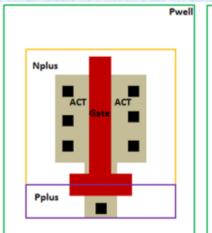

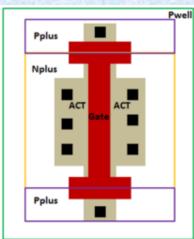

由于埋氧层的存在,SOI电路抗总剂量辐射(TID)能力比体硅电路相对较弱。同时考虑场氧化物对器件总剂量辐射响应的贡献,在SOI材料和工艺方面通过离子注入技术降低了绝缘埋层中所俘获正电荷的数量,降低了SOI器件的总剂量效应敏感度;并在器件结构设计上我们采用了新型器件T、H栅结构,它能够在有体接触的一侧消除寄生边缘漏电路径,,减小总剂量辐射下的漏电水平。本论文采用的130nm SOI工艺已经对浅沟槽隔离(STI)和埋氧层进行了抗总剂量辐射工艺加固,超过300 krad(Si)。

Floating-body layout

T-Gate layout

**H-Gate layout**

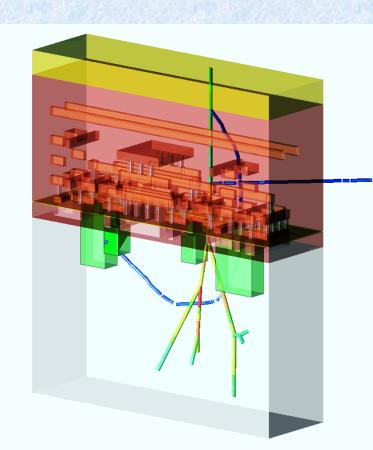

#### 2. SOI平台单粒子效应设计加固

空间辐射环境所导致的高单粒子翻转效应是航天器工作异常和故障的重要诱因之一,必须针对SEU效应的进行高可靠设计。

在RISC-V处理器中,可以将内部电路结构分为两大类,一种是组合逻辑,另一种就是寄存器。SEU可以使得电路中任意一个节点发生翻转,由于组合逻辑中的错误在SEU效应消失后即可恢复为正确的值,所以不会对芯片的功能产生影响。但是由于寄存器具有存储数据的功能,如果打翻的节点位置发生在寄存器单元内部,在SEU效应消失以后,错误仍然会存在。

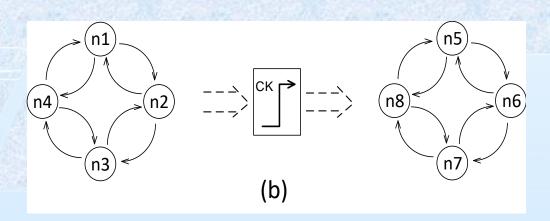

为了提高抗SEU效应的性能,在130nm SOI工艺平台中开发了基于双互锁存储单元 (DICE) 技术的寄存器单元。它的基本思想是将基本的2节点存储结构改进为4节点的存储结构,通过采用单管反相器构成反馈环,当单粒子轰击到任意存储节点时,可以由其他3个节点对翻转的信号进行修复。单粒子效应试验结果表明,DICE寄存器单元的线性能量转移 (LET) 阈值大于37MeV·cm²·mg-1

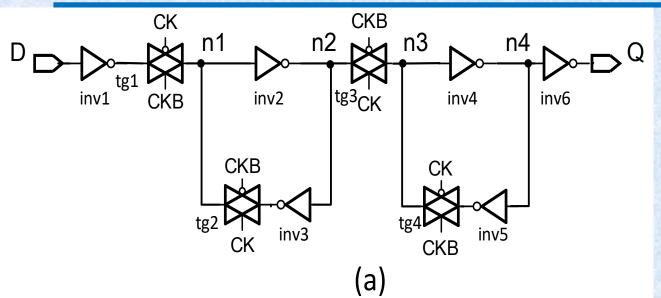

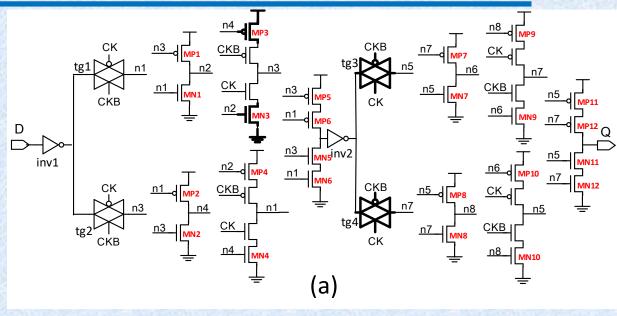

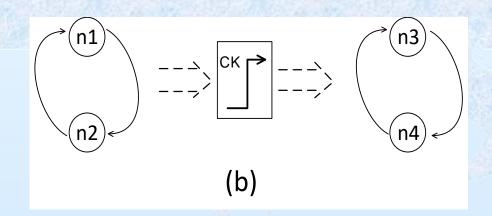

# 2.改进的高可靠加固DICE寄存器单元

标准D触发器电路

DICE触发器电路

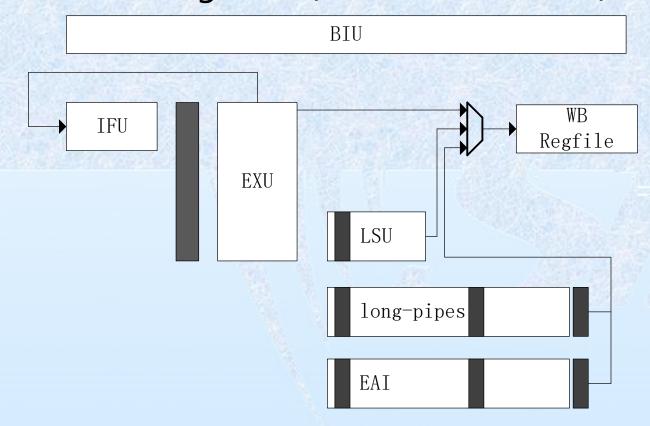

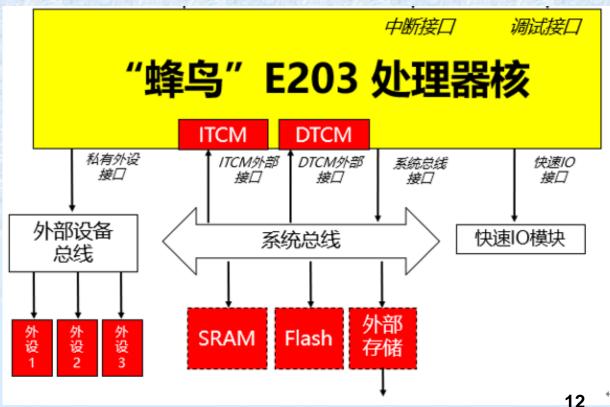

#### 3. 高可靠嵌入式RISC-V设计

本论文中的高可靠低功耗嵌入式通用32位RISC-V处理器SOC是基于开源内核蜂鸟E203设计,采用了两级流水线结构,支持RV32I/A/M/C指令子集的配置组合,支持机器模式 (Machine Mode Only),具有64KB ITCM,64KB DTCM,并提供丰富的外围接口电路支持PWM,SPI,QSPI,GPIO,UART,I2C,WatchDog,RTC(Real Time Counter),Timer

## 3. 高可靠嵌入式RISC-V SOC特性

|   |     | 特性                          | 描述                     |

|---|-----|-----------------------------|------------------------|

|   | CPU | ● 芯片的频率 (MHz) 区间            | 8~50MHz                |

|   |     | ● RISC-V超低功耗2级流水线处理器核       | 支持RISC-V 32位 I/A/M/C指令 |

|   |     | ● 使用标准JTAG调试接口              | eclipse IDE 支持         |

| Ī |     | ● 支持GDB交互式软件调试能力            | eclipse IDE 支持         |

|   |     | ● 支持中断控制器                   | CLINT, PLIC            |

|   | 存储  | ● 片上ITCM-SRAM (指令)          | 64KB                   |

|   |     | ● 片上DTCM-SRAM (数据)          | 64KB                   |

|   |     | ● 可通过QSPI接口外接其他片外存储         | 片外Nor Flash/FeRAM      |

|   | 外设  | ● 提供PWM                     | 3组                     |

| ı |     | ● 提供SPI, QSPI               | 3组                     |

| ı |     | ● 提供GPIO                    | 32个pin脚                |

| ı |     | ● 提供UART                    | 2组                     |

|   |     | ● 提供I2C                     | 1组                     |

| ı |     | ● 提供WatchDog                | 1组                     |

|   |     | ● 提供RTC (Real Time Counter) | 1组                     |

|   |     | ● 提供计时器 (Timer)             | 1组                     |

### 3. 高可靠嵌入式RISC-V SOC设计实现

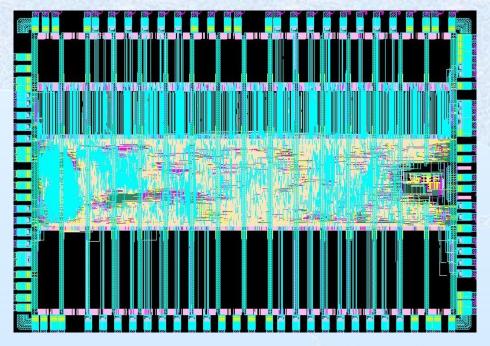

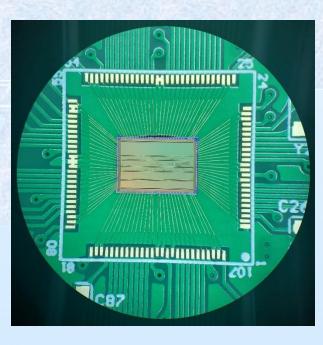

在130nm 1P7M SOI工艺上设计实现,针对高能粒子所引起的三种辐射效应: SEL、SEU和TID分别作了高可靠设计,并把相关设计的加固单元集成在了标准单元库内用于高可靠RISC-V处理器的设计使用。对于高可靠RISC-V处理器的设计,电路设计层主要是通过DICE结构寄存器以及多模冗余实现。相比于未采用加固设计的单元,加固冗余设计需要占用更大的面积,这加大了芯片后端设计的难度,特别是在如何减小芯片的面积方面,需要进行仔细的考量与优化。处理器内核的面积约为13.7mm²,处理器内核加上IO接口的面积约为14.8mm²。

## 3. 流片测试结果

初步测试结果表明,该处理器功能正常,能够在50MHz频率下稳定工作,且功耗小于50mW,总剂量大于300 krad(Si),单粒子SEL免疫

```

int a message before the PLL enabled, Core freq at 15999598 Hz

fter PLL configuration, starting PLL.

Print a message after the PLL enabled, Core freq at 47998533 Hz

nis is printf function printed by jason.sun:

##### #

ase enter any letter from keyboard to continue!

int a message before the PLL enabled, Core freq at 15999565 Hz

fter PLL configuration, starting PLL...

Print a message after the PLL enabled, Core freq at 47998500 Hz

ore freq at 47998500 Hz

K performance run parameters for coremark

otal ticks : 377935886

otal time (secs): 11533.687500

terations/Sec : 0.069362

ompiler flags : -02 -fno-common -funroll-loops -finline-functions --param max-inline-insns-auto=20

-falign-functions=4 -falign-jumps=4 -falign-loops=4

mory location : STACK

edcrc : 0xe9f5

crcmatrix

: 8x1fd7

: 0x8e3a

]crcstate

orrect operation validated. See readme.txt for run and reporting rules.

oreMark 1.0 : 0.069362 / GCC7.2.0 -02 -fno-common -funroll-loops -finline-functions --param max-inli

-insns-auto=20 -falign-functions=4 -falign-jumps=4 -falign-loops=4 / STACK

int Personal Added Addtional Info to Easy Visual Analysis

So the CoreMark/MHz can be caculated by:

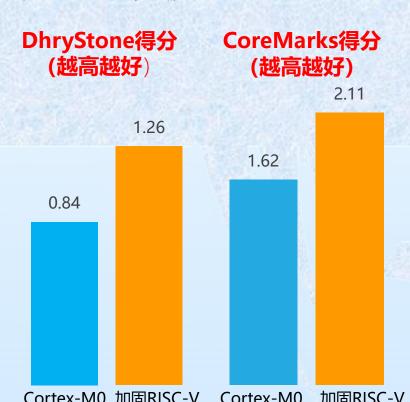

(Iterations*1000000/total_ticks) = 2.116761 CoreMark/MHz

Program has exited with code:0x00000000

```

```

Print a message before the PLL enabled, Core freg at 15999270 Hz

After PLL configuration, starting PLL...

2.Print a message after the PLL enabled, Core freq at 47998369 Hz

Core freq at 47998369 Hz

Dhrystone Benchmark, Version 2.1 (Language: C)

Program compiled without 'register' attribute

Please give the number of runs through the benchmark:

Execution starts, 3200000 runs through Dhrystone

Execution ends

Final values of the variables used in the benchmark:

should be:

Bool Glob:

should be:

Ch_1_Glob:

should be:

2 Glob:

should be:

rr_1_Glob[8]:

should be:

Arr_2_Glob[8][7]:

3200010

should be:

Number_Of_Runs + 10

etr Glob->

Ptr_Comp:

-1879032544

should be:

(implementation-dependent)

Discr:

should be:

Enum_Comp:

should be:

Int_Comp:

should be:

Str_Comp:

DHRYSTONE PROGRAM, SOME STRING

should be:

DHRYSTONE PROGRAM. SOME STRING

Next_Ptr_Glob->

Ptr_Comp:

should be:

(implementation-dependent), same as above

Discr:

should be:

Enum_Comp:

Int Comp:

should be:

Str_Comp:

DHRYSTONE PROGRAM, SOME STRING

should be:

DHRYSTONE PROGRAM, SOME STRING

nt_1_Loc:

should be:

Int_2_Loc:

should be:

Int 3 Loc:

should be:

num Loc:

should be:

DHRYSTONE PROGRAM, 1'ST STRING

should be: DHRYSTONE PROGRAM, 1'ST STRING

Loc: DHRYSTONE PROGRAM, 2'ND STRING

should be: DHRYSTONE PROGRAM, 2'ND STRING

(*) User_Cycle for total run through Dhrystone with loops 3200000:

So the DMIPS/MHz can be caculated by:

1000000/(User_Cycle/Number_Of_Runs)/1757 = 1.264782 DMIPS/MHz

Program has exited with code:0x00000000

```

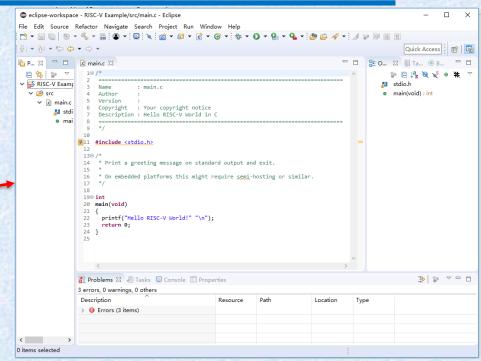

## 3. 完整的RISC-V工具链与软件开发环境

- C/C++ Compiler

- Standard GNU GCC Toolchain (with both Linux and Windows version), 调试工具链、 中断控制器

- Windows and Linux IDE

- Eclipse C/C++ Development IDE

- Software Simulation

- Based on QEMU

- JTAG Debugger

- JTAG Debugger (FTDI)

- RTOS Support

- FreeRTOS

- RT-Thread

本论文首次采用130nm SOI工艺进行高可靠嵌入式RISC-V处理器的设计和流片验证。该处理器采用开源指令集RISC-V内核蜂鸟E203,在SOI工艺加固的基础上,通过设计加固以提升抗辐射性能。初步测试结果表明,该处理器功能正常,能够在50MHz频率下稳定工作,且功耗小于50mW,总剂量大于300 krad(Si),单粒子SEL免疫

The end.